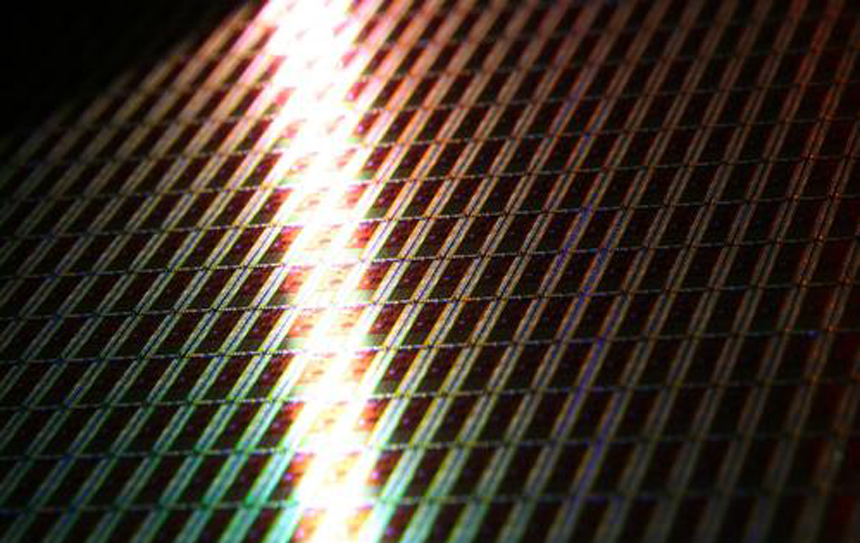

晶圆制造突破战!EUV光刻机加持后,硝烟再起!

文章出处:霍尔开关原创 人气:发表时间:2020-10-29 11:24

对于芯片产业来说,制程工艺是一个大家耳熟能详的一个词。然而随着摩尔定律的限制,不少厂商都在寻找继续突破的办法。为了从22nm过渡到16nm,几乎所有从事半导体制造的领头羊企业都选择从平面晶体管转为FinFET晶体管,由平面转向立体。

然而目前半导体制程面临的又一大壁垒则是5nm,要突破到5nm以下,就不得不选择全新的解决思路,比如使用极紫外光刻机(EUV)等,然而不同的半导体厂商纷纷踏上了不同的罗马大路。

三星

三星为了化身半导体行业的领军人,去年正式发布了“2030愿景”战略,在2030年之前投资133万亿韩元(1105.1亿美元)。如今三星已在做出了一系列举措,比如开发3nm工艺、投资神经处理单元与AMD合作开发移动GPU等。三星如今已在韩国与美国建立了先进的300mm晶圆厂,在韩国和中国苏州也有测试和封装的产线。

三星将借助EUV在FinFET上实现5nm和4nm,目前三星也在加快第三个EUV节点的量产计划。而到了3nm上,三星将采用全新的GAA(环绕式栅极)结构。最典型的GAA就是纳米线,但由于纳米线的高成本,三星设计了一种全新的GAA形式MBCFET。MBCFET由多层堆叠的纳米片组成,从FinFET的横向堆叠改为垂直堆叠,兼容已有的FinFET设计。三星计划2020年提供首批3nm GAA工艺客户流片,2020年末进行试产,2021年末正式进入量产。

在三星的规划中,14nm制程将作为低成本的首选,主要用于存储、小芯片、DDR4和PCIe 4等应用;8nm主打性价比,已经可以用于AI交互、DDR5、PCIe 5和GPU,比如英伟达最新的RTX30系列。5nm和4nm则主要用于下一代CPU、AI训练,并实现112G的SerDes速率,采用2.5D、3D TSV和FOWLP等先进封装。三星在汽车上使用的先进工艺主要是14nm与8nm,提供AEC-Q100和ASIL B/D的认证,以及MIPI、内存、PCIe、以太网和安全等应用上的关键IP,辅以低成本高性能的封装。

英特尔

英特尔的制程迭代之路就比较坎坷,不过与广大代工厂不同的是,他们并不需要保持制程优势,只要能在维持竞争力的情况下满足客户需求即可。因此Intel在14nm上徘徊了很长时间,直到2019年的处理器才开始使用10nm制程,而今年又爆出了7nm制程出现问题,产品线全面延迟,甚至解雇了芯片业务的主要负责人,甚至在考虑未来是寻求代工合作还是购买更多的7nm设备。这主要归结于EUV的使用过晚,和技术业务架构上的失误。

作为最早实现FinFET的厂商之一,Intel并不想在制程上落后于人,但他们更重视于晶体管密度的提升而不是单单的制程升级。今年8月,英特尔正式公布了10nm下的SuperFin技术,用于下一代Tiger Lake芯片中,并保证其功耗效率可以与台积电的7nm相抗衡。在今年的第三季度财报会议上,Intel CEO司瑞博提到他们已经找到了7nm工艺问题的根源,部署了解决方案,取得了惊人的进展。此外,Intel在今年提出未来五年内将采用GAA结构,但他们所用的正是三星所抛弃的纳米线。从Intel的路线图来看,GAA结构也许会用于5nm制程工艺中。

台积电

台积电目前5nm制程已经实现量产,专门针对移动应用以及高效能运算应用开发。该制程为台积电第二代运用极紫外(EUV)技术的制程,早在去年3月就已经进入了试产阶段,于今年开始量产。目前苹果的A14芯片以及华为海思的麒麟9000系列芯片都采用了台积电的5nm制程,未来AMD的Zen 4 CPU也将使用这一技术。此外台积电预计5nm推出一年后,将推出5nm FinFet强化版制程技术N5P,提升5%的性能,降低10%的功耗。

而5nm之后,台积电打算先推出N4制程,通过进一步部署EUV层来减少光罩,并将芯片设计者的移植工作量减少到最小。台积电预计N4的试产将于2021年第四季度开始,量产则要等到2022下半年,因此我们也许只能在2023年才得以看到4nm芯片登场。而在3nm节点上,台积电并不打算采用GAA结构,而是继续维持在FinFET。台积电强调,他们对现有的FinFET技术打造了显著的升级,使其能够达到下一代的性能表现。台积电还提到了FinFET的可预见性能使他们在批准时间线内成功交付该制程下的产品。这句话也许才是台积电固守FinFET的根本原因,作为晶圆代工厂,满足客户的交期才是最关键的目标。而GAA这种先进结构,未知性太大,一旦产量和良率无法保证,将对公司造成巨大的打击。

中芯国际

中芯国际目前第一代14nm的FinFET已经取得了突破,并在2019年第四季度进入了量产阶段,也是目前大陆自主研发集成电路的最高制程水平。尽管中国大陆的制程工艺比较落后,但中芯国际在更先进制程上的研发早就开始了。中芯国际从28nm直接进入14nm,跳过了20nm的节点,未来也很有很可能直接实现制程飞跃。

2017年底,中芯国际就已经开始投入研发资金开发7nm工艺。中芯国际的N+1与N+2制程并没有宣称是7nm,也不会采用EUV工艺。只有等到设备就绪后,N+2后的制程将使用EUV进一步推进制程迭代。今年10月11日,主营业务为IP和定制芯片的芯动科技宣布已经完成了基于中芯国际FinFET N+1工艺的芯片流片和测试。据高盛预测,中芯国际在2022年可以成功过渡到7nm工艺,2024年下半年将可以实现5nm工艺。

从几大公司的研发投入来看,制程突破不仅耗时,而且耗财。像英特尔这样的IDM芯片厂商,出现制程问题后,都触发了一系列负面影响,更不用说其他代工厂了。与此同时,芯片制程的迭代不代表对过去技术的完全抛弃,最新的制程仍将是高性能的代名词,也是AI、5G、自动驾驶等技术的陪绑宣传,但其余制程下的产品仍将在各个应用领域中生根发芽,这也是为什么台积电还在推出N12e新制程的原因。国内虽然起步较晚,但是随着制程工艺的推进愈发困难,相信未来很快就会迎头赶上。

下一篇:霍尔元件在防盗报警器上的应用 上一篇:霍尔开关在电脑上的应用

同类文章排行

- 霍尔元件的BOP和BRP什么意思

- 影响霍尔元件灵敏度的因素有哪些

- 霍尔元件管脚如何定义和接线?

- 霍尔元件损坏的原因可能有哪些?

- 霍尔开关损坏的原因分析

- 迪仕科技与小米集团合作签约

- 霍尔元件NPN常开常闭和PNP常开常闭的区别

- 霍尔元件选型指南(入门篇)

- 霍尔开关应该如何接线

- 什么是线性霍尔元件

最新资讯文章

- 霍尔开关DH220/DH553在智能跳绳上的应用

- 霍尔元件代工厂华虹半导体连续刷新营收纪录

- 三星将参与收购Arm?

- 芯片厂商不敢要求降价,只求明年涨幅减半

- 消费电子芯片恐将遭受暴击型降价

- 日本被动元件,称霸全球

- 砍单潮下,芯片过剩、库存高企问题显现

- 张忠谋:解决芯片荒问题,有一个办法

- 台积电已向美国提交两份机密文件

- 日资30年电子厂关闭,称已“完成使命”

- 光刻机:美国是如何发明并彻底失去的

- 苹果A16弃3nm?业界曝关键

- Model 3零部件国产化率2年超90%,芯片呢?

- 霍尔元件的性能是如何测试的?

- 霍尔元件的应用发展分析

- 美国没有光刻机背后的原因

- 要跟Wi-Fi说再见了?

- 客户库存调整!盛群:Q4订单仍供不应求

- ST意法半导体:半导体需求热到明年

- 满坤科技积极布局PCB下游领域

苏公网安备32021302001984

苏公网安备32021302001984